來源:半導體行業觀察

爲滿足AI服務器先進封裝的產能需求,台積電正在摩拳擦掌。

在七月的業績會議上, $台積電 (TSM.US)$ 董事長魏哲家也在回應分析師有關先進封裝的CoWoS產能緊張的議題時提到,人工智能火爆帶動了CoWoS需求,台積電CoWoS需求非常強,台積電持續擴增2025-2026年希望達到供需平衡,CoWoS的資本支出目前無法明確說明,因爲每年都在努力增加,上次已提到今年產能超過翻倍成長,公司也非常努力地在擴充產能。

爲了踐行這個目標,台積電封裝正在瘋狂擴產。

爲了踐行這個目標,台積電封裝正在瘋狂擴產。

買廠,建廠,台積電擴產不停

在臺積電的封裝擴張路線上,早前購入的群創南科4廠,廠房代號爲AP8廠區會是公司封裝發展的一個明智選擇。因爲通過這單交易,將省去須以年計的環評階段,這也公司預計能在明年下半年將該工廠投產。據臺媒表示,該廠的未來產能比竹南先進封裝廠大9倍,且將納入晶圓代工與3D IC。

今年8月中旬,台積電宣佈斥資171.4億新臺幣,購入群創位在南科的5.5代LCD面板廠,該廠原本爲記憶體大廠美光屬意,一直到台積電、群創重訊公佈廠房交易訊息,外界才知道台積電已經搶先一步。

供應鏈透露,台積電會購入群創南科4廠的最主要原因,就是省去以年計算的環評步驟,與嘉義的先進封裝廠不同,只要進行廠內改裝工程,不到1年機臺進駐後就可以投產。

設備端業者指出在廠房交易案確定後,台積電就針對AP8廠啓動建廠計畫,目標在2025年下半年投產,相關的機臺設備製造訂單同步進行,預期明年4月陸續交機,約1季的試產,下半年投產並不難。

由於AP8廠的規模比竹南先進封裝廠大9倍,供應鏈認爲不會只有先進封裝的CoWoS產能,未來先進製程的晶圓代工、扇出型封裝以及3D IC等產線都有可能會進駐。

除了買下工廠,台積電之前的建廠也在穩步推進。

今年五月,進駐嘉義科學園區的台積電CoWoS先進封裝廠正是動工,但在施工過程中挖到了疑似遺址,現依據文資法進行相關處理,外界關切該廠進展。但臺灣方面表示,預計文資法相關清理工作將於今年10月完成,台積電嘉科先進封裝廠規劃明年第3季裝機不受影響。

根據先前規劃,台積電將在嘉義設2座CoWoS先進封裝廠,原計劃2028年量產。具體到工藝方面,據報道,這個廠主要以系統整合單芯片(SoIC)爲主,台積電也較看好3D封裝,目前客戶包括芯片大廠超微( $美國超微公司 (AMD.US)$ )MI300外,至2026年客戶有望進一步提升。

而由於CoWoS需求旺盛,台積電還在全臺尋覓適合的擴廠據點,早前規劃的銅鑼廠遭遇水土方面問題,而嘉義第一座廠則暫時卡關(挖到遺址),着眼長期龐大需求,驅使台積電需要提早尋求更多匹配的地點。先前媒體報導,雲林縣長張麗善指出,縣府已自主啓動「虎尾產業園區計劃」,在所在位置緊鄰中科虎尾園區,面積約29.75 公頃的情況下,全力爭取台積電落腳設廠。

但最近有消息指出,除近期購買的南科周遭土地,台積電建廠廠址決定捨棄雲林轉往屏東。台積電表示,設廠地點選擇有諸多考量因素,不排除任何可能性。在今年年初,甚至還有消息透露,晶圓代工龍頭台積電正考慮在日本建立先進封裝廠,這足以看到這項封裝技術的受歡迎程度。

美系法人預估,台積電的CoWoS月產能到年底可能超過3.2萬片,若加上協力廠商有機會逼近4萬片,到2025年底月產能約在7萬片上下。

台積電營運、先進封裝技術暨服務副總何軍在半導體展時也透露,預期CoWoS先進封裝產能在2022至2026年,年複合成長率達到50%以上,到2026年仍會持續擴產,以往3至5年蓋一個廠,現在已縮短到2年內就要蓋好,以滿足客戶需求。

DIGITIMES研究中心在八月中發表的《AI芯片特別報告》中指出,先進封裝成長力道更勝先進製程,在先進封裝領域,AI芯片高度仰賴台積電CoWoS封裝技術,因此台積電2023~2028年CoWoS產能擴充CAGR將超過50%,而2023~2028年晶圓代工產業5nm以下先進製程擴充年均複合成長率將達23%。

在產能大幅提升的同時,台積電也在迭代公司的封裝技術,以求爲客戶提供更多的支持。

封裝技術的持續升級

在最近爲北美客戶舉辦的研討會上,這家芯片製造商公佈了芯片封裝和尖端光學互連技術的雄心勃勃的路線圖。這些進步可能會在未來幾年掀起計算性能的浪潮。

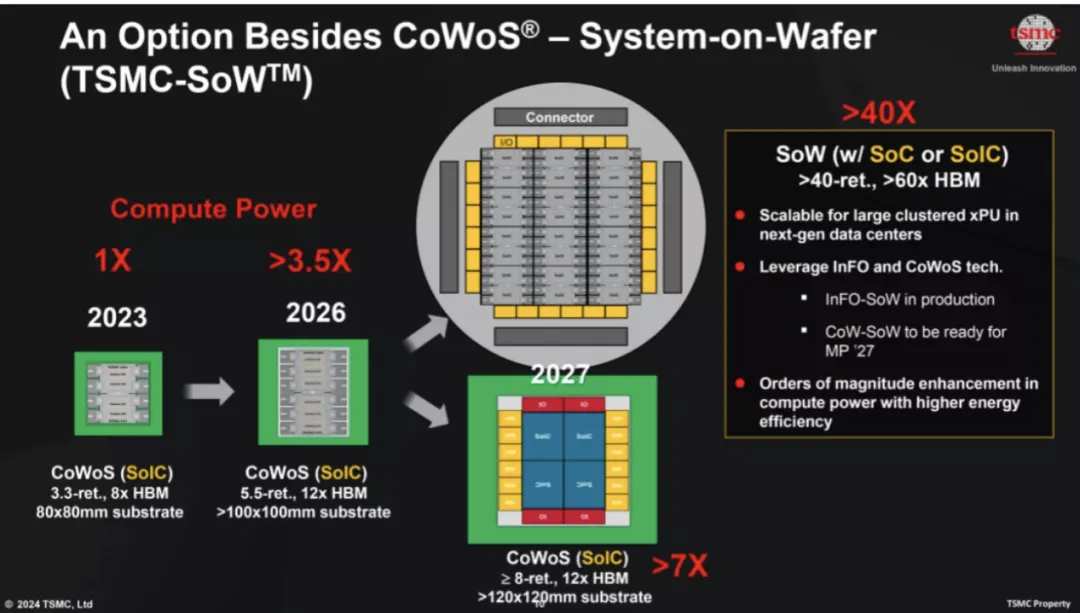

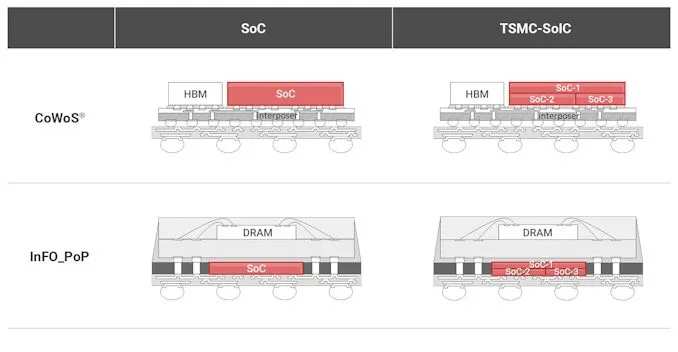

首先是芯片封裝技術,台積電將其命名爲「CoWoS」(晶圓基板上的芯片),它本質上是典型小芯片設計的增強版,其中多個較小的芯片集成到一個封裝中。但台積電正在將其提升到令人難以置信的規模和複雜性的新水平。

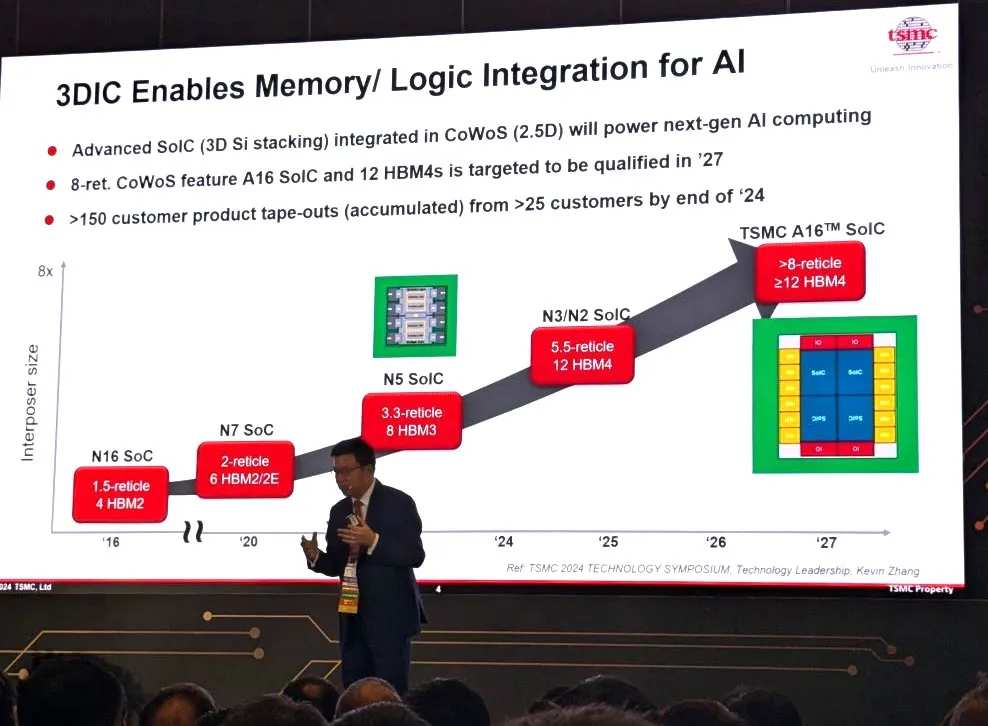

當前的 CoWoS 迭代支持中介層(硅基層)的尺寸高達光刻中使用的典型光掩模的 3.3 倍。但到 2026 年,台積電的「CoWoS_L」將使其尺寸增加到大約 5.5 倍的掩模尺寸,爲更大的邏輯芯片和多達 12 個 HBM 內存堆棧留出空間。而僅僅一年後的 2027 年,CoWoS 將擴展到令人瞠目結舌的 8 倍掩模版尺寸甚至更大。

我們談論的是集成封裝,面積達 6,864 平方毫米,比一張信用卡大得多。這些 CoWoS 龐然大物可以整合四個堆疊邏輯芯片以及十幾個 HBM4 內存堆棧和額外的 I/O 芯片。

爲了讓您了解其規模,$博通 (AVGO.US)$同時還展示了一款定製的 AI 處理器,該處理器具有兩個邏輯芯片和 12 個內存堆棧。該芯片看起來比$英偉達 (NVDA.US)$ 最新的強大加速器還要大。據介紹,這個採用了太極丹晶圓基板芯片 (CoWoS) 封裝技術的芯片具有接近光罩極限(858 平方毫米,26 毫米 x 33 毫米)的計算芯片。

但與台積電爲 2027 年準備的芯片相比,這個芯片仍然微不足道。因爲如上所述,台積電預計其解決方案將使用高達 120x120 毫米的基板。

在臺積電的封裝版圖裏,3D IC毫無疑問將扮演重要角色。

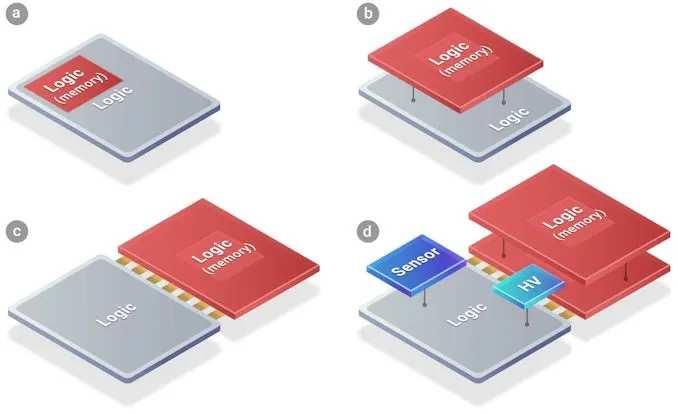

同樣是在今年的技術研討會上,台積電概述了一份路線圖,到 2027 年,該技術將從目前的 9μm 凸塊間距一路縮小到 3μm 間距,將 A16 和 N2 芯片組合堆疊在一起。

據介紹,台積電的3D 堆疊集成芯片系統 (SoIC) 技術是台積電對混合晶圓鍵合的實現。混合鍵合允許將兩個先進的邏輯器件直接堆疊在一起,從而實現兩個芯片之間的超密集(和超短)連接,主要針對高性能部件。目前,SoIC-X(無凸塊)用於特定應用,例如 AMD 的 CPU 3D V 緩存技術,以及他們的 Instinct MI300 系列 AI 產品。雖然採用率正在增長,但當前這一代技術受到芯片尺寸和互連間距的限制。

但如果一切按照臺積電的計劃進行,這些限制預計很快就會消失。SoIC-X 技術將快速發展,到 2027 年,將有可能組裝一個芯片,將台積電尖端 A16(1.6 納米級)上製造的掩模版大小的頂部芯片與使用台積電 N2(2 納米級)生產的底部芯片配對。這些芯片將依次使用 3μm 鍵合間距硅通孔 (TSV) 連接,密度是當今 9μm 間距的三倍。如此小的互連將允許總體上更大的連接數量,從而大大提高組裝芯片的帶寬密度(從而提高性能)。

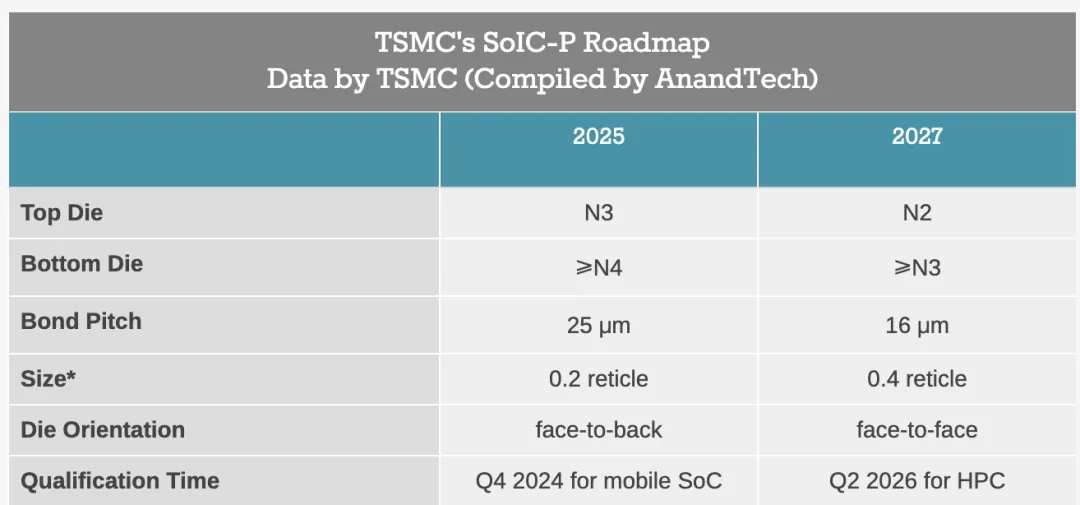

除了針對需要極高性能的設備開發無凸塊 SoIC-X 封裝技術外,台積電還將在不久的將來推出凸塊 SoIC-P 封裝工藝。SoIC-P 專爲更便宜的低性能應用而設計,這些應用仍需要 3D 堆疊,但不需要無凸塊銅對銅 TSV 連接帶來的額外性能和複雜性。這種封裝技術將使更廣泛的公司能夠利用 SoIC,雖然台積電不能代表其客戶的計劃,但更便宜的技術版本可能會使其適用於更注重成本的消費者應用。

根據台積電目前的計劃,到 2025 年,該公司將提供正面對背面 (F2B) 凸塊 SoIC-P 技術,該技術能夠將 0.2 光罩大小的 N3(3 納米級)頂部芯片與 N4(4 納米級)底部芯片配對,並使用 25μm 間距微凸塊 (µbump) 進行連接。2027 年,台積電將推出正面對背面 (F2F) 凸塊 SoIC-P 技術,該技術能夠將 N2 頂部芯片放置在間距爲 16μm 的 N3 底部芯片上。

爲了讓 SoIC 在芯片開發商中更受歡迎、更容易獲得,還有很多工作要做,包括繼續改進其芯片到芯片接口。但台積電似乎對行業採用 SoIC 非常樂觀,預計到 2026 年至 2027 年將發佈約 30 種 SoIC 設計。

據臺灣媒體集邦引述台積電先進封裝技術與服務副總裁何軍在早前的semicon taiwan演講中的報道,台積電認爲,3D IC是將AI芯片存儲器與邏輯芯片集成的關鍵方法。何軍也指出,預估2030年全球半導體市場將成爲萬億產業,其中HPC與AI爲關鍵驅動力,佔比達40%,這也讓AI芯片成爲3D IC封裝的關鍵驅動力。

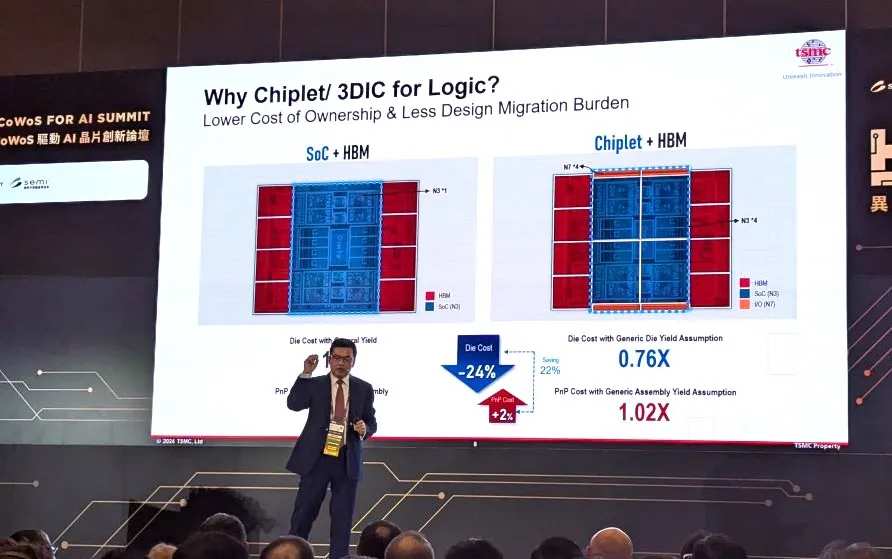

何軍表示,客戶選擇使用 3D IC 平台進行多芯片設計製造 AI 芯片的原因與其較低的成本和減少的設計轉換負擔有關。

何軍解釋說,通過將傳統的SoC+HBM設計轉換爲chiplet和HBM架構,新的邏輯芯片將是唯一需要從頭設計的組件,而I/O和SoC等其他組件可以使用現有的工藝技術。這種方法可將量產成本降低高達76%。他指出,雖然新的架構可能會增加2%的生產成本,但由於這些效率的提高,總體擁有成本(TCO)提高了22%。

不過,3D IC仍面臨挑戰,尤其在差能提升方面,何軍強調,提升3D IC產能的關鍵在於芯片尺寸以及製程複雜度。至於芯片尺寸,更大的芯片可以容納更多的芯片,從而提高性能。然而,這也增加了工藝的複雜性,難度可能增加三倍。此外,還存在與芯片錯位、破損和提取過程中故障相關的風險。

爲了應對這些風險挑戰,何君確定了三個關鍵因素:工具自動化和標準化、過程控制和質量、以及3DFabric製造平台的支持。

對於工具自動化和標準化,台積電與其工具供應商的差異化能力至關重要。目前,台積電擁有 64 家供應商,已具備在先進封裝工具領域處於領先地位的能力。在製程管控與品質方面,台積電採用高分辨率PnP工具與AI驅動的品質管控,確保全面且穩健的品質管理,最後以3DFabric製造平台整合供應鏈內1,500種材料,實現優化。

光電封裝,台積電的下一個目標

在大力發展傳統電封裝的時候,光也成爲了台積電的關注點。

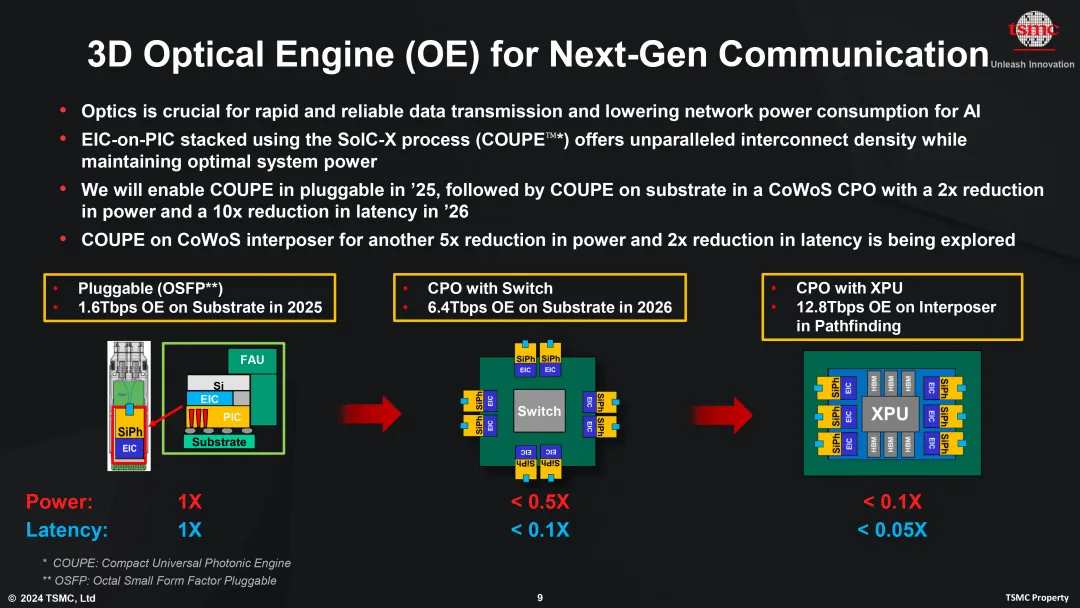

今年的技術研討會上,台積電同時還透露了其「3D Optical Engine」戰略,旨在將閃電般快速的光學互連集成到其客戶設計中。隨着帶寬需求的激增,銅線根本無法滿足前沿數據中心和 HPC 工作負載的需求。利用集成硅光子學的光學鏈路可提供更高的吞吐量和更低的功耗。

台積電表示,公司正在開發緊湊型通用光子引擎 (COUP:Compact Universal Photonic Engine) 技術,以支持 AI 熱潮帶來的數據傳輸爆炸式增長。COUPE 使用 SoIC-X 芯片堆疊技術將電子芯片堆疊在光子芯片之上,從而在芯片間接口處提供最低阻抗,並且比傳統堆疊方法具有更高的能效。台積電計劃在 2025 年使 COUPE 獲得小型可插拔器件的認證,隨後在 2026 年將其作爲共封裝光學器件 (CPO) 集成到 CoWoS 封裝中,將光學連接直接引入封裝中。

通過採用先進的 3D 堆疊技術,台積電將電子器件和光子器件封裝在一起。第一代產品以 1.6 Tbps 的速度插入標準光纖端口,是目前高端以太網的兩倍。第二代產品通過將 COUPE 與處理器一起集成到台積電的 CoWoS 封裝中,將速度提升至 6.4 Tbps。路線圖的最終成果是 CoWoS「COUPE 中介層」設計,其光纖帶寬達到驚人的 12.8 Tbps。

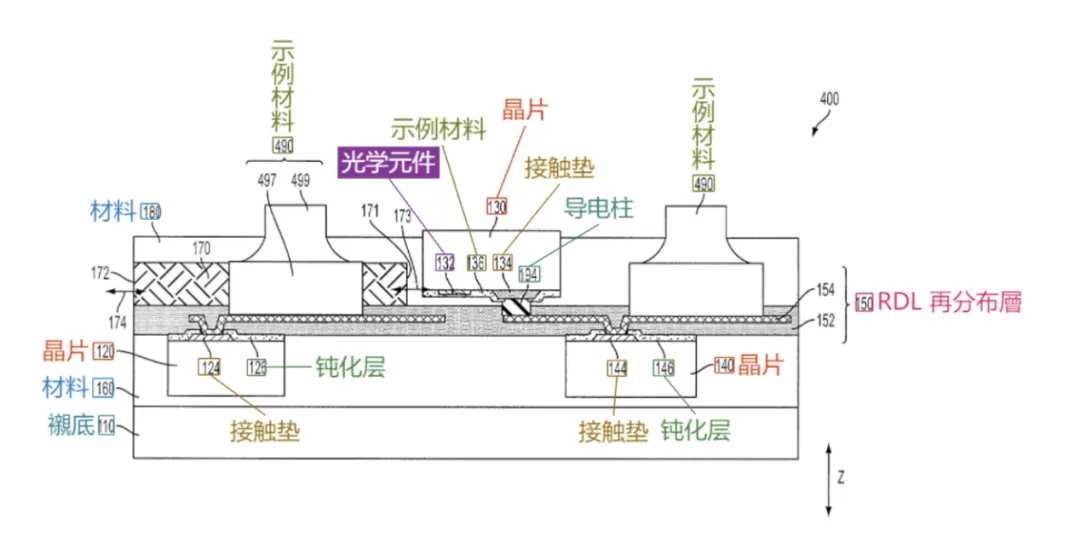

關於台積電的硅光技術,雖然公司最近才宣佈了規劃。但根據臺媒報道,他們其實很早就在這上面有佈局。

臺媒表示,通過利用incoPat 專利資料庫檢索CPO 共同封裝光學的專利技術現狀,發現台積電早已在此技術領域開展布局,並且目前也是此領域的主要專利權人之一。例如早在2013年臺積電就提出US9423578B2專利,提出使用光信號代替電信號進行數據傳輸,以解決在各種類型的IC中使用的電信號也受到IC中的電容,電感或電阻引起的增加的延遲的影響。由於此技術提出的時間較早,目前也成爲許多其他專利的前案。

本月初,台積電還參與建立了一個硅光聯盟,爲這個技術的普及打下了紮實的基礎。

台積電副總總經理徐國晉在聯盟成立的致詞中提到,整個半導體產業歷經60、70年發展,從不同的元件設計,逐漸聚焦CMOS(互補式金屬氧化物半導體)元件技術開發應用,這也是硅光子所利用的製程技術,對光子、電子進行整合。他指出,當CMOS成爲商業應用主流後,產業發展不管在產品設計研發,上下游分工也更明確,尤其節能是很大優勢。

徐國晉認爲,目前光學元件、硅光子元件還在比較初期的百花齊放階段,隨着AI時代需要的巨量運算、數據傳輸大量需求,耗能成爲重要議題,硅光子元件的導入成爲數據中心重要趨勢。

從上述的報道中我們也能看到,這家前道巨頭,已經成爲封裝領域當之無愧的巨無霸。

編輯/Rocky

为了践行这个目标,台积电封装正在疯狂扩产。

为了践行这个目标,台积电封装正在疯狂扩产。