預計2023-2026年,台積電非晶圓收入的複合年增長率(CAGR)將達到31%;Rubin架構或採用3D SoIC封裝技術。

$台積電 (TSM.US)$最近可謂動作不斷,從提高先進製程價格,到進軍“方形基板”。

最近,摩根士丹利發佈了一份關於台積電的報告,詳細總結了CoWos、PLP技術和3D SoIC的最新進展。

• CoWos封裝:台積電預計,到2026年底,每月的CoWoS晶圓產能將達到約6萬片;與先前披露的2024年底CoWoS封裝產能將達到2.6-2.8萬片/月相比,翻了一倍多;

• 面板級(PLP)封裝:該技術與近期市場關注的“方形基板”相關。目前正在研發階段,大規模量產還需數年時間;

• 3D SoIC封裝:預計從2025年下半年開始增加產能,Rubin架構或採用3D SoIC封裝技術。

一、CoWoS 產能更新

在最近的技術研討會上,台積電表示:從2022年到2026年,CoWoS技術的產能預計將以超過60%的年複合增長率迅速增長。到2026年底,每月的CoWoS晶圓產能將達到約6萬片。

目前,台積電的CoWoS月產能約爲1.5萬片,預計到2024年底,這一數字將提升至每月2.6-2.8萬片。

同時,2024年全年,台積電計劃投資280-320億美元,其中約10%將用於先進封裝技術。

摩根士丹利分析師指出,強勁的封裝需求將成爲未來幾年台積電非晶圓收入快速增長的主要驅動力:

• 預計2023-2026年,台積電非晶圓收入的複合年增長率(CAGR)將達到31%;

• 到2023年,非晶圓銷售有望佔到台積電總收入的13%;

1)CoWoS-L封裝

摩通指出,台積電正在加速其CoWoS技術的擴展,重點放在適應越來越大尺寸的AI芯片需求上,特別是CoWoS-L技術。

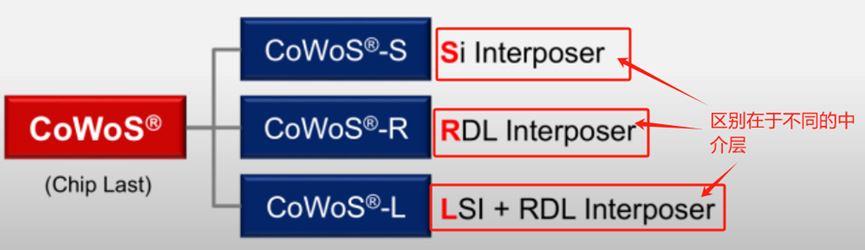

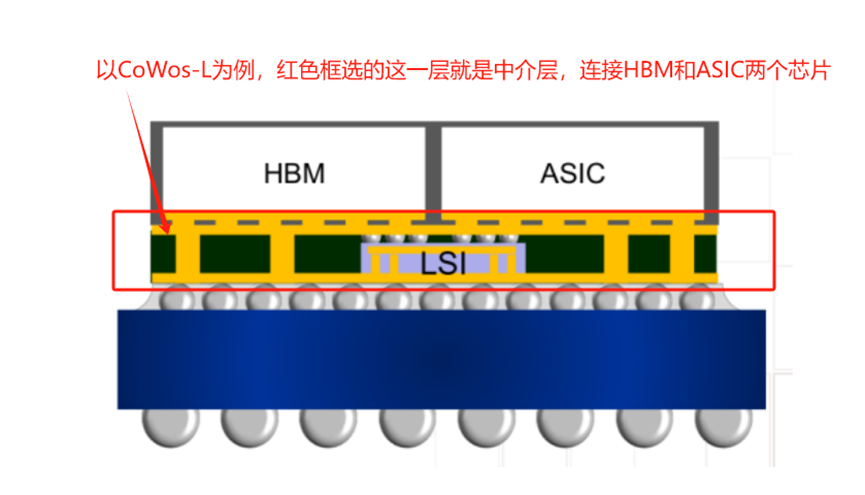

CoWoS封裝技術現分爲三種類型:CoWoS-S、CoWoS-R和CoWoS-L,它們的主要區別在於中介層的設計,這是連接芯片的關鍵層。

隨着人工智能芯片尺寸的增加,先前使用硅中介層的CoWoS-S技術出現了良率問題。

爲了應對這一挑戰,台積電推出了CoWoS-L技術,採用了LSI+RDL中介層,有效解決了大尺寸芯片的良率問題。

摩通預計,未來臺積電在CoWoS技術的發展將主要聚焦於CoWoS-L,以應對日益擴大的AI芯片面積需求。

二、面板級(PLP)封裝技術

摩通指出,台積電正在進行面板級(PLP)封裝技術的研究,但大規模量產還需要幾年時間。

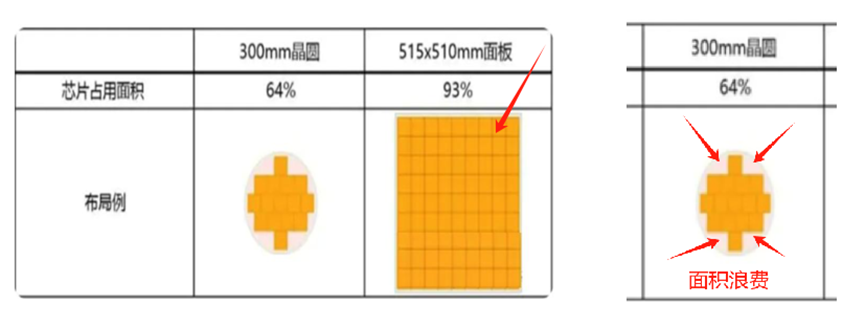

PLP封裝是一種將晶粒重新排列在更大的矩形面板上的封裝方案(見下圖左側)。

目前,台積電使用的是圓形晶圓基板,這導致了面積的浪費(見下圖右側)。

據《日經亞洲》報道,由於AI帶來的計算需求激增,台積電正在探索510㎜ × 515㎜的矩形基板。

矩形基板的有效面積比圓形晶圓大三倍以上,有望顯著提升台積電的生產能力。

然而,與圓形基板相比,方形基板存在光刻膠塗布不均勻和易碎裂的問題。

摩通指出,要實現PLP封裝技術的大規模量產,仍需要數年時間的技術攻關。

三、3D SoIC先進封裝

3D SoIC是台積電開發的先進封裝技術,專注於實現高密度的芯片垂直堆疊(相比之下,CoWoS技術主要是橫向堆疊)。

摩通指出,目前3D SoIC技術在市場上還相對較爲小衆,只有AMD在其Ryzen 3D和MI300 AI加速器中採用。

預計從2025年下半年開始,台積電將逐步增加3D SoIC的產能。到2025年底,預計每月的3D SoIC產能將達到大約12,000到14,000片晶圓;到2026年底,預計將增至每月20,000片晶圓。

此外,摩通推測,英偉達的Rubin架構以及蘋果的M5處理器可能會採用3D SoIC技術。

編輯/Somer